What is the initialization process

This section explains the behavior of the Cortex-A9 single processor, from the reset exception to the main() function. The main() function works with secure world privileges (Refer to #15), with the memory space set to normal memory cacheable for 1 M bytes of RAM space starting at 0x8000000, while the rest of the memory space is set to “Strong Order Memory (see Part 10)”. The virtual and physical addresses are set as the same address in the “MMU (reference 12)” as the same address.

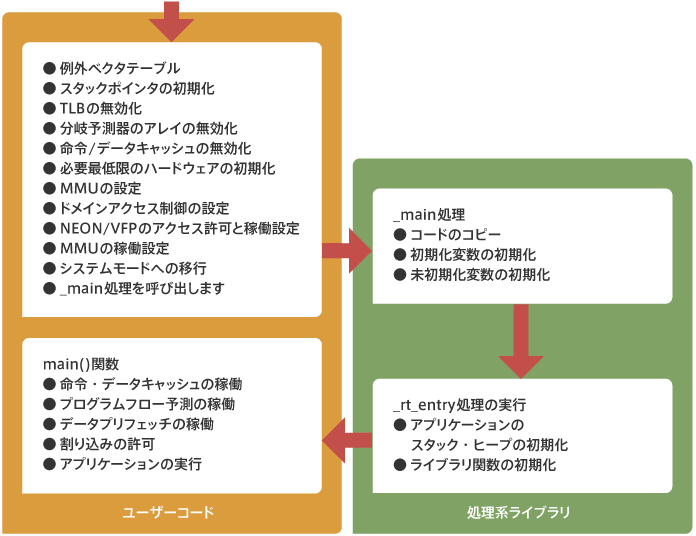

The initialization from the reset exception to the call of the main() function can be divided into two parts: the part created by the user (user code) and the part executed by the Arm compiler (processor libraries). Copying the code and initialization of initialized/uninitialized variables is done by the implementation library, which executes the linker’s memory allocation settings (scatter loading description file settings).

Exception Vector Table

The exception vector table describes a branch instruction of the Arm instruction (32-bit) and FIQ interrupts are placed at the last address of the exception vector table, so you can write interrupt handlers directly. For more information, see See “6: Vector Tables and Exceptions” for details.

AREA VECTORS,CODE,READONLY ; Define sections as VECTORS areas.

ENTRY

;====================================================================

; exception vector table

;====================================================================

EXPORT Start ; for setting the image entry point.

Start ; Image entry address setting

LDR PC,reset_addr ; Reset exception

LDR PC,undefined_addr ; undefined instruction

LDR PC,svc_addr ; supervisor call exception

LDR PC,prefetch_addr ; prefetch abort exception

LDR PC,abort_addr ; Data abort exception

B . ; Reserved vector table

LDR PC,irq_addr ; IRQ interrupt

LDR PC,fiq_addr ; FIQ interrupt

;====================================================================

; Execution Start Processing Address Definition

;====================================================================

reset_addr DCD reset_handler ; Reset Exception Handler Address Definition

undefined_addr DCD undefined_handler ; Undefined instruction exception handler address definition

svc_addr DCD svc_handler ; Supervisor Call Exception Handler Address Definition

prefetch_addr DCD prefetch_handler ; Prefetch Abort Exception Handler Address Definition

abort_addr DCD abort_handler ; Data Abort Exception Handler Address Definition

irq_addr DCD irq_handler ; IRQ interrupt handler address definition

fiq_addr DCD fiq_handler ; FIQ interrupt handler address definition

undefined_handler

B undefined_handler ; Permanent loop in case of undefined instruction exception

svc_handler

B svc_handler ; Permanent loop in the event of a supervisor call exception

prefetch_handler

B prefetch_handler ; Permanent loop in the event of a prefetching exception

abort_handler

B abort_handler ; Permanent loop in case of a data abort exception

irq_handler

B irq_handler ; Permanent loop in case of IRQ interrupt generation

fiq_handler

B irq_handler ; Permanent loop in case of FIQ interrupt generation

Initialization of stack pointer

The stack pointer must be set up for each operating mode, so initialize the stack pointer after switching the operating mode. The memory space used by the stack pointer is set in the scatter loading description file. The user stack pointer is set by the processor library and does not need to be initialized. For more information, see “5: Operation Mode“.

;==================================================================== ; CPSR mode setting flag definition ;==================================================================== MODE_USR EQU 0x10 ; CPSR.mode[4:0] User mode setting value MODE_FIQ EQU 0x11 ; CPSR.mode[4:0] FIQ mode setting MODE_IRQ EQU 0x12 ; CPSR.mode[4:0] IRQ mode setting value MODE_SVC EQU 0x13 ; CPSR.mode[4:0] Supervisor mode setting MODE_ABT EQU 0x17 ; CPSR.mode[4:0] Abort mode setting MODE_UND EQU 0x1B ; CPSR.mode[4:0] Undefined mode setting MODE_SYS EQU 0x1F ; CPSR.mode[4:0] System mode setting value ;==================================================================== ; Refer to the stack address from the scatter loading description file ;==================================================================== IMPORT ||Image$$IRQ_STACK$$ZI$$Limit|| ; IRQ mode stack final address IMPORT ||Image$$FIQ_STACK$$ZI$$Limit|| ; FIQ Mode Stack Final Address IMPORT ||Image$$UND_STACK$$ZI$$Limit|| ; last address of undefined mode stack IMPORT ||Image$$ABT_STACK$$ZI$$Limit|| ; abort mode stack last address IMPORT ||Image$$SVC_STACK$$ZI$$Limit|| ; supervisor mode stack last address reset_handler ;==================================================================== ; Initialize each mode stack ;==================================================================== CPS #MODE_IRQ ; Switch to IRQ mode LDR SP, =||Image$$IRQ_STACK$$ZI$$Limit|| ; Initializing the IRQ mode stack CPS #MODE_FIQ ; Switch to FIQ mode LDR SP, =||Image$$FIQ_STACK$$ZI$$Limit|| ; Initializing the FIQ mode stack CPS #MODE_UND ; Change to undefined mode LDR SP, =||Image$$UND_STACK$$ZI$$Limit|| ; Initialize the undefined mode stack CPS #MODE_ABT ; Switch to abort mode LDR SP, =||Image$$ABT_STACK$$ZI$$Limit|| ; Initialize the abort mode stack CPS #MODE_SVC ; Switch to supervisor mode LDR SP, =||Image$$SVC_STACK$$ZI$$Limit|| ; Initializing the supervisor mode stack

Example of scatter loading description file

- In the scatter loading description file, the program starts at

0x80000000and the stack pointer starts at0x80088000, allocating 16K bytes of stack area for each operating mode. - The first level table is located at

0x800F0000. - The source file name for the initialization process is set to

startup.s. - The user mode stack is set by the processor library in the

Arm_LIB_STACKsetting. - The heap area is set by the processor library in the

Arm_LIB_HEAPsetting.

LOAD 0x80000000 0x20000000

{

VECTORS 0x80000000 {

startup.o(VECTORS,+FIRST) ; Place the vector code area

*(+RO)

*(+RW)

*(+ZI)

}

;

; 0x80080000

;

Arm_LIB_HEAP 0x80080000 ALIGN 8 EMPTY 0x8000 {

}

Arm_LIB_STACK +0 ALIGN 8 EMPTY 0x4000 {

}

IRQ_STACK +0 ALIGN 8 EMPTY 0x4000 { ; IRQ Mode Stack

}

FIQ_STACK +0 ALIGN 8 EMPTY 0x4000 { ; FIQ Mode Stack

}

UND_STACK +0 ALIGN 8 EMPTY 0x4000 { ; undefined mode stack

}

ABT_STACK +0 ALIGN 8 EMPTY 0x4000 { ; abort mode stack

}

SVC_STACK +0 ALIGN 8 EMPTY 0x4000 { ; supervisor mode stack

}

TTB 0x800F0000 EMPTY 0x4000 { ; first level table

}

}

| Address Space | Arrangement Details | Size |

|---|---|---|

| 0x800F0000-0x800F3FFF | Placing the first level table | 16K bytes |

| 0x800A0000 to 0x800EFFFF | Unused space | – |

| 0x8009C000-0x8009FFFF | Privileged mode stack region (SVC_STACK) | 16K bytes |

| 0x80094000-0x80097FFF | The undefined mode stack region (UND_STACK) | 16K bytes |

| 0x80090000-0x80093FFF | FIQ Mode Stack Region (FIQ_STACK) | 16K bytes |

| 0x80080080000-0x8008FFFF | IRQ mode stack region (IRQ_STACK) | 16K bytes |

| 0x80088000-0x8008BFFF | User mode stack area (Arm_LIB_STACK) | 16K bytes |

| 0x80080080080000-0x80087FFF | Application heap area (Arm_LIB_HEAP) | 32K bytes |

| 0x80000000 to 0x8007FFFF | Program area (VECTORS) | 512K bytes |

Disable TLB (Translation Look-Aside Buffer)

Convert from a virtual address to a physical address using TLBs and disable TLBs as they are cached. For details, see 13th: Coprocessor Settings” for details.

MOV r0, #0 ; MCR p15, 0, r0, c8, c7, 0 ; Disabling TLB

Disabling the array of branch predictors

Disables the Branch Target Address Cache (BTAC). For more information, see 13th: Coprocessor Configuration Example” for details.

MOV r0, #0 ; MCR p15, 0, r0, c7, c5, 6 ; Disabling the Branch Predictor Array

Disable instruction/data cache

Disable the instruction/data cache on reset. For more information, see 13th: Coprocessor Configuration Example” for details.

;

; L1 data cache setting (32Kbyte/4Way)

;

CACHE_LINE EQU 0xFF ; Number of data cache lines

CACHE_WAY EQU 4 ; Number of data cacheways

;====================================================================

; Disabling the instruction cache

;====================================================================

MOV r0, #0 ;

MCR p15, 0, r0, c7, c5, 0 ; Disabling the instruction cache

;====================================================================

; Disabling the data cache

;====================================================================

MOV r1,#CACHE_LINE ; Set the number of lines (256 lines)

Loop2

MOV r0,#CACHE_WAY ; Set the number of ways (4 ways)

Loop3

MOV r2, r0, LSL #30 ; Set the way number

ORR r3, r2, r1, LSL #5 ; Set the line number

MCR p15, 0, r3, c7, c6, 2 ; Disable cache lines in set/way settings

SUBS r0, r0, #1 ; Way number -1.

BGE Loop3 ; Initialization on a per-way basis

SUBS r1, r1, #1 ; Set the set number to -1.

BGE Loop2 ; Initialization of each set

Setting up the MMU

Use the Address Translation Using First Level Tables function to initialize the virtual and physical addresses as the same address. For more information, see “Part 12: MMU” for more information.

PAGE_TABLE_STRONGLY EQU 2_00000000000000000000110111100010

PAGE_TABLE_NORMAL EQU 2_00000000000000000001110111101110

TTBR0_SETTING EQU 0x48

IMPORT ||Image$$TTB$$ZI$$Base|| ; Refer to the top address of the TLB table.

;====================================================================

; Cortex-A9 MMUコンフィギュレーション設定

;====================================================================

MOV r0, #0x0 ;

MCR p15, 0, r0, c2, c0, 2 ; Conversion table-based control (TTBCR) initialization

LDR r0,=||Image$$TTB$$ZI$$Base|| ; Set the TLB base address.

MOV r1, #TTBR0_SETTING ;

ORR r0,r0,r1 ; Set the setting of TTBR0.

MCR p15, 0, r0, c2, c0, 0 ; Write to conversion table base 0 (TTBR0)

;====================================================================

; Created in level 1 conversion table format (4,096 1Mbytes of virtual memory space to control)

;====================================================================

LDR r0, =||Image$$TTB$$ZI$$Base|| ; Set the first address of the TLB.

LDR r1, =0xFFF ; Initialize counters

LDR r2, =PAGE_TABLE_STRONGLY ; Initial Page Table Settings

init_ttb_1

ORR r3, r2, r1, LSL#20 ; Set the base address

STR r3, [r0, r1, LSL#2] ; TLB writes

SUBS r1, r1, #1 ; Reduce the counter to -1.

BPL init_ttb_1 ; End of entry table creation?

;====================================================================

; Vector area Sets the page table entry.

;====================================================================

LDR r1, =||Image$$VECTORS$$Base|| ; Set the first address of the TLB.

LSR r1, #20 ; Set the address on a 1MB boundary.

LDR r2, =PAGE_TABLE_NORMAL ; normal memory

ORR r3, r2, r1, LSL#20 ; Find the initial value of TLB

STR r3, [r0, r1, LSL#2] ; Updating the Page Table

Configure Domain Access Control

Set the Domain Access Control Register to initialize it to all client settings. For more information, see “Part 12: MMU” for details.

;====================================================================

; Set the domain access control register for all clients.

;====================================================================

LDR r0, =0x55555555 ; All Client Settings

MCR p15, 0, r0, c3, c0, 0 ; Domain Access Control Register (DACR) writing

NEON/VFP Permissions and Availability Settings

Configure the access rights and availability of the coprocessor (NEON/VFP). For details, see 13th: Coprocessor configuration example.

;====================================================================

; Enforce NEON/VFP access permissions (allowing CP10/CP11 access)

;====================================================================

MRC p15, 0, r0, c1, c0, 2 ; Read Coprocessor Access Control Register (CPACR)

ORR r0, r0, #(0xF ≪ 20) ; Full access settings for CP10/11

MCR p15, 0, r0, c1, c0, 2 ; Write to the coprocessor access control register (CPACR)

ISB ;

;====================================================================

; NEON/VFP action starts.

;====================================================================

MOV r0, #0x40000000 ;

VMSR FPEXC, r0 ; Set the EN bit in the floating-point exception register

Setting up the MMU

Since the MMU is set to inactive at reset, it should be enabled after all settings are complete. For more information, see “Part 12: MMU” for details.

;====================================================================

; Set the MMU to operational status.

;====================================================================

MRC p15,0,r0,c1,c0,0 ; Read SCTLR

ORR r0,r0,#0x1 ; Set the MMU to active (SCTLR.M[0])

MCR p15,0,r0,c1,c0,0 ; Writing to SCTLR

DSB ; Terminate all memory accesses.

ISB ; Execution of instruction synchronization barriers

calling the main() function from the library initialization execution

After the initialization process, execute the processor library and call the main() function in “System mode (See Part 5)” and calls the main() function. The initialization process runs with the instruction/data cache disabled, so it runs the instruction/data cache, program flow prediction, and data prefetch functions. It then initializes the peripherals, permits interrupts, and changes the operating mode of the processor to user mode (unprivileged) if necessary.

Finally

We hope that all 17 APS ACADEMY ACADEMY introductory sessions have been helpful to you in your development. I hope you find it helpful as you begin your development. Finally, I would like to thank all those who have supported the APS ACADEMY Cortex-A Introductory Edition for the past year and five months of writing. I would like to thank the members of my workplace for their various contributions. Finally, I would like to thank my family for their support of my writing.

July 2015 auspicious date

殿下信二

“もっと見る” カテゴリーなし

Mbed TLS overview and features

In this article, I'd like to discuss Mbed TLS, which I've touched on a few times in the past, Transport …

What is an “IoT device development platform”?

I started using Mbed because I wanted a microcontroller board that could connect natively to the Internet. At that time, …

Mbed OS overview and features

In this article, I would like to write about one of the components of Arm Mbed, and probably the most …